|

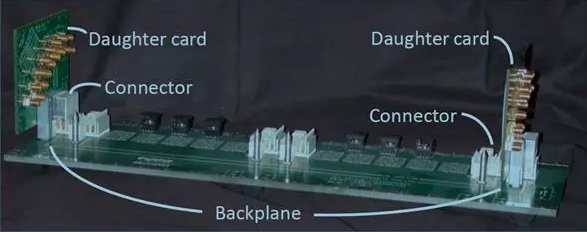

加速你的设计进程 | 高速通道建模、仿真及眼图的嵌入和去嵌测试信号完整性是分析和缓解高速数字链路中噪声、失真和损耗所带来的负面影响的系统工程,是高速链路性能和系统级可靠性的重要保障。 然而如何保障电气性能的完整却是高速电路“攻城狮”的一大难题。熟练的“老鸟”们总能够应用信号完整性理论,合理地使用仿真和测试工具,快速地解决各种电路的问题。 今天我们就来跟大家聊聊这其中的工具,并提供手把手的视频让大家的技术“突飞猛进”。 在高速数字信号传输中,通道指的是从发射端IO Buffer到接收端IO Buffer之间的电子路径。它可能由芯片的封装,PCB板上的走线,连接器和线缆组成。一个简单的通道可以从发射端IO Buffer,PCB走线到接收端IO Buffer。 一个复杂的通道(例如背板)由图1所示元件组成。

图1. 一个大约20英寸长的通道 在进行通道建模的时候 需要注意三个最重要的特性 1.阻抗;2.损耗;3.延时或者相位 阻抗取决于机械结构,介电常数和金属导电性。阻抗不匹配将造成多重反射,最终导致信号振铃、过冲和下冲。 另外通道损耗对SERDES设计很关键,信号损失的主要原因是介电损耗和导体损耗,而这些损耗通常是依赖于频率的。从而一个信道的频带宽度限制了其可通过的最大比特率。对于DDR来说,命令、地址和时钟或DQ和DQS之间的相位差必须被很好的控制。

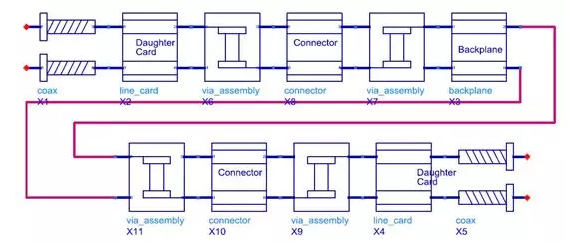

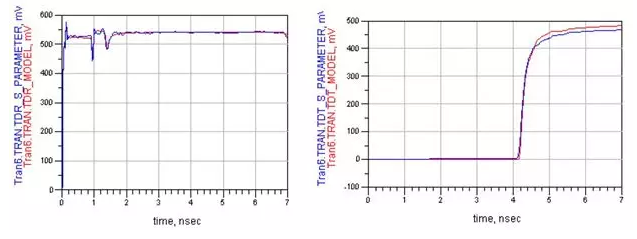

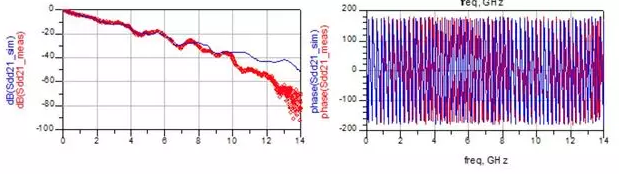

图2. 一个通道中的不同元件 通道的元件可以用基于公式的传输线模型、电磁模型或者基于测量的模型建模。对于每个元件的建模正确与否取决于尺寸以及材料参数是否精确。元件模型准确定义好之后,把这些元件级联起来构建一个完整的通道模型(如图2所示),就可以通过TDR仿真来估计通道的阻抗和时延(如图3所示)。通道的插入损耗可以通过S参数仿真估计(如图4所示)。最终这些仿真结果将为“攻城狮”改善通道性能、支持更高速率传输提供调试优化线索。

图3.阻抗变化(左)和时延(右)

图4. 插入损耗(左)和相位(右) 关键字:探针台,晶圆探针台,Cascade探针台,去嵌测试 版权声明:本文转载自网络。若有侵权,请联系我公司删除。 |